機能通信センシング(赤澤研究グループ)

Masamichi Akazawa

| 研究者氏名 | 赤澤正道 |

|---|---|

| アカザワ マサミチ | |

| 所属 | 北海道大学 |

| 部署 | RCIQE - 機能通信センシング |

| 職名 | 准教授 |

| 学位 | 博士(工学)(北海道大学) |

論文

Control of plasma-CVD SiO2/InAlN interface by ultrathin atomic-layer-deposited Al2O3 interlayer

Masamichi Akazawa and Shouhei Kitajima

Jpn. J. Appl. Phys. 58(SI) SIIB06-1-SIIB06-8 2019年8月 [査読有り]

Masamichi Akazawa and Kei Uetake

Jpn. J. Appl. Phys. 58(SC) SCCB10-1-SCCB10-6 2019年6月 [査読有り]

Kazuki Isobe and Masamichi Akazawa

AIP Advances 8(11) 115011-1-115011--6 2018年11月 [査読有り]

Masamichi Akazawa and Taito Hasezaki

Phys. Status Solidi B 255(5) 1700382- 1-1700382- 6 2018年5月 [査読有り]

M. Akazawa, N. Yokota, and K. Uetake

AIP Advances 8(2) 025310-1-025310-7 2018年2月 [査読有り]

M. Akazawa, N. Yokota, and K. Uetake

AIP Advances 8(2) 025310-1-025310-7 2018年2月 [査読有り]

Masamichi Akazawa and Atsushi Seino

Phys. Status Solidi B 254(8) 1600691-1-1600691-6 2017年8月 [査読有り]

M. Matys, B. Adamowicz, A. Domanowska, A. Michalewicz, R. Stoklas, M. Akazawa, Z. Yatabe, and T. Hashizume

J. Appl. Phys. 120(22) 225305-1-225305-12 2016年12月 [査読有り]

Interface control technologies for high-power GaN transistors: Self-stopping etching of p-GaN layers utilizing electrochemical reactions

T. Sato, Y. Kumazaki, M. Edamoto, M. Akazawa and T. Hashizume

Proceeding of SPIE 9748, Gallium Nitride Materials and Devices XI 97480Y-1-97480Y-7 2016年2月 [査読有り]

Process-dependent properties of InAlN surface and ALD-Al2O3/InAlN interface

M. Akazawa, M. Chiba, and T. Nakano

Extended Abstracts of 2014 International Conference on Compound Semiconductor Manufacturing Technology (CSMANTECH 2014, Sheraton Downtown Denver, Denver, Colorado, USA, May 19-22, 2014) 313-316 2014年5月

M. Chiba, T. Nakano, and M. Akazawa

Phys. Status Solidi C 11(3-4) 902-905 2014年4月 [査読有り]

T. Nakano, M. Chiba, and M. Akazawa

Jpn. J. Appl. Phys. 53(4) 04EF06-1-04EF06-5 2014年4月 [査読有り]

M. Akazawa and T. Nakano

e-Journal of Surface Science and Nanotechnology 12 83-88 2014年3月 [査読有り]

Effects of High-Temperature Annealing on Properties of Al2O3/InAlN Interface Formed by Atomic Layer Deposition

T. Nakano, M. Chiba, and M. Akazawa

Extended Abstracts of 2013 International Conference on Solid State Devices and Materials (SSDM2013, Hilton Fukuoka Sea Hawk, Fukuoka, Japan, Sept. 25-27, 2013) PS-6-3-1-PS-6-3-2 2013年9月 [査読有り]

M. Akazawa, M. Chiba, and T. Nakano

Appl. Phys. Lett. 102(23) 231605-1-231605-3 2013年6月 [査読有り]

M. Akazawa and T. Nakano

Jpn. J. Appl. Phys. 52(6) 08JN23-1-08JN23-3 2013年5月 [査読有り]

T. Nakano and M. Akazawa

IEICE Trans. Electron. E85- C(5) 686-689 2013年5月 [査読有り]

M. AKAZAWA and T. NAKANO

Appl Phys Lett 101(12) 122110-122110-4 2012年9月 [査読有り]

M. Akazawa and T. Nakano

ECS Solid State Letters 1(1) 4-6 2012年7月 [査読有り]

Effect of hydrofluoric acid treatment on InAlN surfaces

T. Nakano and M. Akazawa

Workshop Digest of 2012 Asia-Pacific Workshop on Fundamental and Applications of Advanced Semiconductor Devices (AWAD2012, Naha, Okinawa, Japan, June 27-29, 2012) 242-246 2012年6月 [査読有り]

M. Akazawa, B. Gao, T. Hashizume, M. Hiroki, S. Yamahata, and N. Shigekawa

Phys. Status Solidi C 9(3-4) 592-595 2012年3月 [査読有り]

M. Akazawa, B. Gao, T. Hashizume, M. Hiroki, S. Yamahata, and N. Shigekawa

Phys. Status Solidi C 8(7-8) 2139-2141 2011年7月 [査読有り]

AKAZAWA M., GAO B., HASHIZUME T., HIROKI M., YAMAHATA S., SHIGEKAWA N.

Appl Phys Lett 98(14) 142117 2011年4月 [査読有り]

AKAZAWA M., GAO B., HASHIZUME T., HIROKI M., YAMAHATA S., SHIGEKAWA N.

J Appl Phys 109(1) 013703 2011年1月 [査読有り]

Akazawa Masamichi, Hasegawa Hideki

Applied Surface Science 256(19) 5708-5713 2010年7月 [査読有り]

This paper attempts to realize unpinned high-k insulator-semiconductor interfaces on air-exposed GaAs and In0.53Ga0.47As by using the Si interface control layer (Si ICL). Al2O3 was deposited by ex-situ atomic layer deposition (ALD) as the high-k i...

H. Hasegawa, M. Akazawa, A. Domanowska, B. Adamowicz

Appl. Surf. Sci. 256(19) 5698-5707 2010年7月 [査読有り]

AKAZAWA M., MATSUYAMA T., HASHIZUME T., HIROKI M., YAMAHATA S., SHIGEKAWA N.

Appl Phys Lett 96(13) 132104 2010年3月 [査読有り]

M. Akazawa and H. Hasegawa

Phys. Status Solidi (c) 7(2) 351-354 2010年2月 [査読有り]

M. Akazawa and H. Hasegawa

Phys. Status Solidi C 7(2) 351-354 2010年2月 [査読有り]

HASEGAWA Hideki, AKAZAWA Masamichi

J Korean Phys Soc 55(3,Pt.1) 1167-1179 2009年9月 [査読有り]

HASEGAWA Hideki, AKAZAWA Masamichi

J Vac Sci Technol B 27(4) 2048 2009年7月 [査読有り]

AKAZAWA Masamichi, DOMANOWSKA Alina, ADAMOWICZ Boguslawa, HASEGAWA Hideki

J Vac Sci Technol B 27(4) 2028 2009年7月 [査読有り]

M. Akazawa and H. Hasegawa

Materials Science and Engineering B 165(1-2) 122-125 2009年1月 [査読有り]

AKAZAWA Masamichi, HASEGAWA Hideki

e−Journal Surf Sci Nanotechnol (Web) 7 122-128 2009年 [査読有り]

H. Hasegawa and M. Akazawa

Applied Surface Science 255(3) 628-632 2008年7月 [査読有り]

AKAZAWA Masamichi, HASEGAWA Hideki

J Vac Sci Technol B 26(4) 1569-1578 2008年7月 [査読有り]

HASEGAWA Hideki, AKAZAWA Masamichi

J Vac Sci Technol B 26(4) 1542-1550 2008年7月 [査読有り]

M. Akazawa and H. Hasegawa

Proceedings of 20th International Conference on Indium Phosphide and Related Materials (IPRM08, 25-29 May 2008, Versailles, France) 1-4 2008年5月 [査読有り]

M. Akazawa and H. Hasegawa

phys. stat. sol. (c) 5(9) 2729-2732 2008年5月 [査読有り]

研究内容

窒化物半導体のデバイスプロセスの研究を行っています。 具体的には以下のような研究を行っています。1.Mgイオン打込みしたGaN中に生じる欠陥についての研究

GaNを用いたパワーデバイス作製のためには、Mgイオン打込みによるp型領域の形成が非常に便利なプロセスとして期待されているのですが、現在のところ、難しい技術となっています。これを克服するには、Mgイオン注入により生じるGaN中の欠陥準位についてよく調べ、さらにそれを制御する必要があります。 イオン打込みは半導体中に多くの欠陥を生じます。さらに、結晶欠陥回復とドーパントの活性化のために高温で熱処理する必要がありますが、この段階でも新たな欠陥が生じる可能性があります。私たちは、n型GaNに少ない量のMgイオンを注入し、低い温度の熱処理から初めてだんだんと温度を上げて行く過程で、結晶欠陥がどのように変化していくかを調べています。

図1. Mgイオン注入したGaNの電気的特性を調べるためのMOS構造の作製プロセス。表面付近をよく調べるためにMOS構造を採用。比較のため。熱処理を行わない試料も作製。完成したMOSダイオードに対して容量-電圧特性を測定し、シミュレーションとも併せて欠陥準位の位置を評価。

2.InAlN MOS構造作製プロセスについての研究

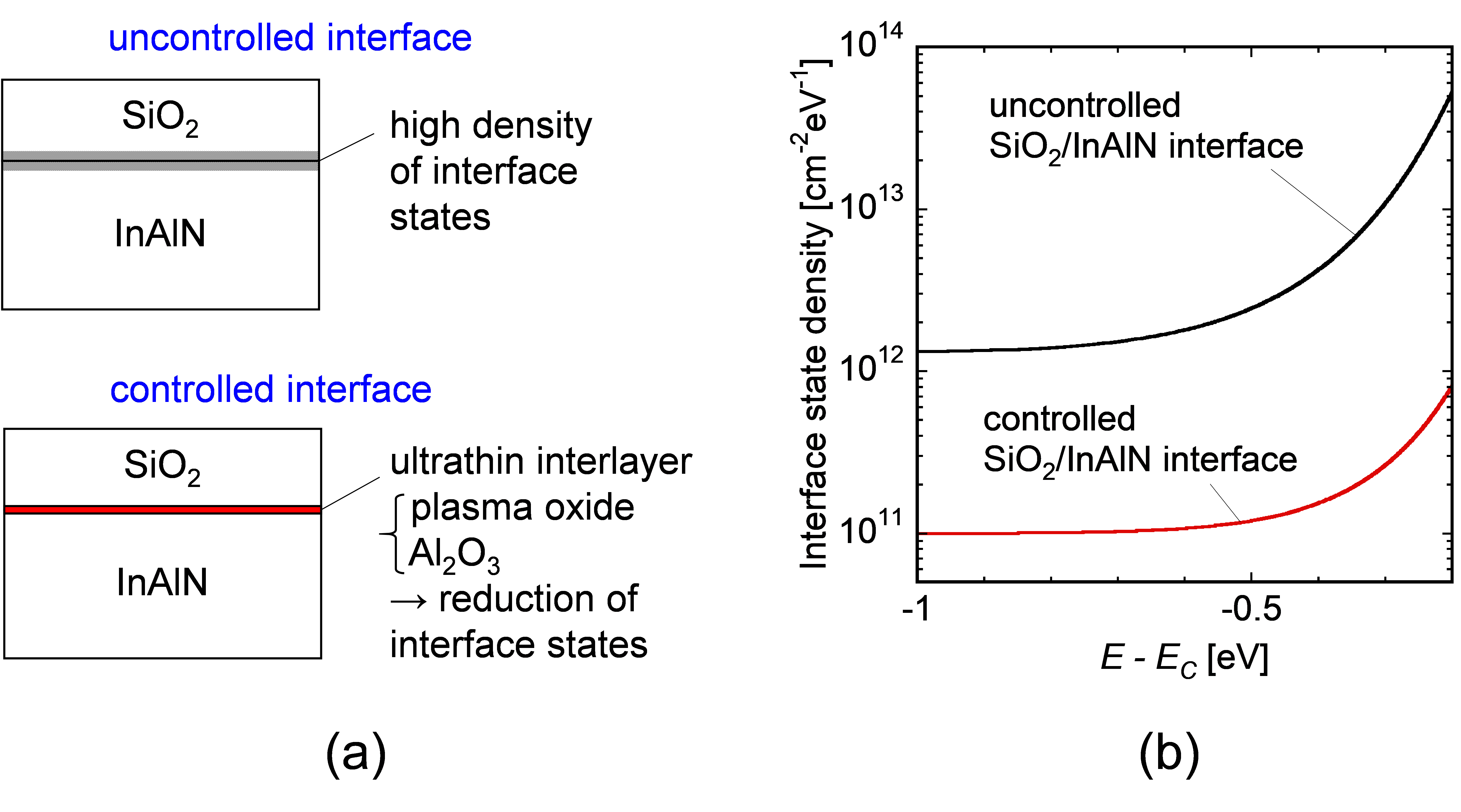

InAlN混晶はGaNに格子整合することができ、大きな自発分極と電子に対する障壁を生じることから、GaN系HEMTの新たなバリア材料として期待されています。しかし、大きな自発分極を有するという特長が逆に短所にもなり、バリア層として用いた時に内部に大きな電界を生じて漏れ電流が大きくなってしまいます。これを解決する1つの方法として絶縁膜を利用したMOSゲート構造とすることが提案されています。しかし、一般には、絶縁体と半導体の界面には界面準位と呼ばれる禁制帯内準位が生じ、MOS構造の電気的特性に悪影響を与えます。 私たちは実用的な絶縁体の中で最も禁制帯幅の大きなSiO2とInAlNとの界面を制御し、界面準位を低減する方法について研究しています。

図2. (a) 介在層挿入によるSiO2/InAlN界面の制御の模式図。(b) 実際に得られた界面準位密度分布。界面の制御によりSiO2/InAlN界面の界面準位密度の低減に成功した例。

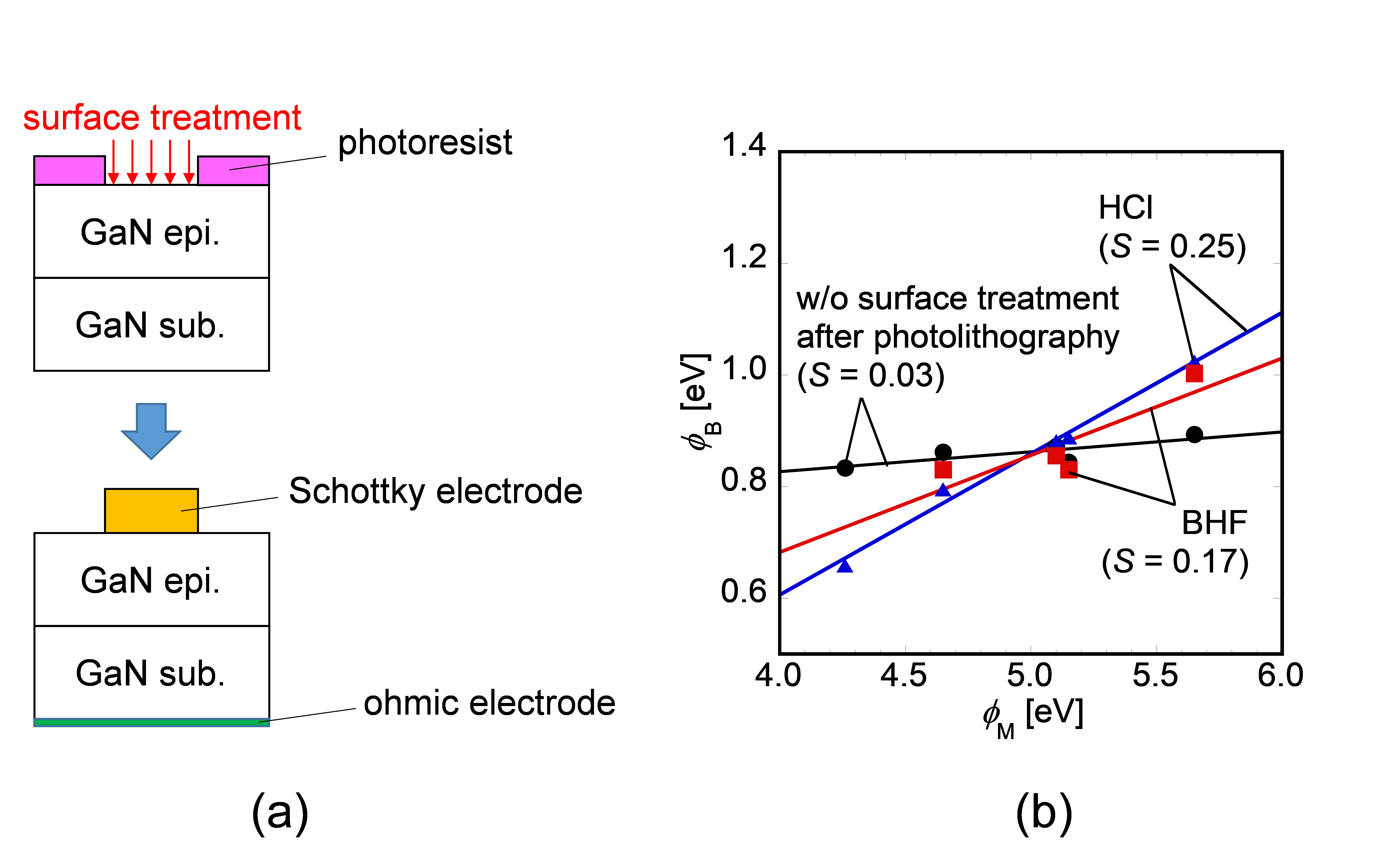

3.金属-GaN界面の形成プロセスについての研究

金属と半導体の界面においては、半導体表面のバンドが曲がり、電子に対する障壁(ショットキー障壁)が生じます。その高さは金属の仕事関数に依存して変化することが期待されるのですが、実際には金属を変えて仕事関数が変わってもショットキー障壁の高さが大きく変化しないのが一般的です。もしこれを、金属の仕事関数に依存してショットキー障壁が変化するように制御することができれば、デバイス設計の自由度が拡大します。 私たちは金属とGaNとの界面を制御し、ショットキー障壁を変化させる方法について研究しています。

図3. (a) ショットキーダイオードに対する表面処理プロセスの模式図。(b) 種々の金属に対して得られたショットキー障壁高ϕBの電極金属仕事関数ϕM依存性。Sは依存性の度合いを示すパラメータでこのプロットの傾きで与えられる。